系统多处采用FPGA,FPGA与DSP均预留开放的配置接口,可供师生进行大量的软件二次开发,同时也便于系统升级。因此,系统除了用于通信原理课程的实验,还可以作为一个开放的硬件平台,用于包括FPGA、DSP、单片机编程在内的各类课程设计和毕业设计。

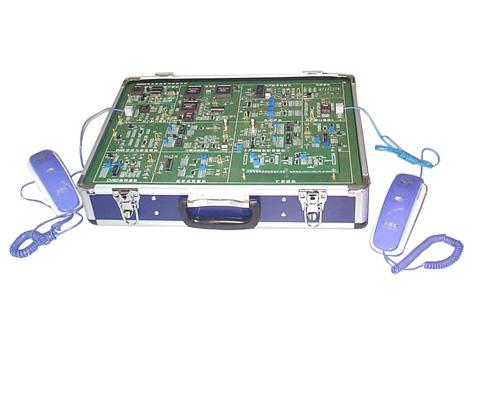

电路硬件平台的基本组成JH5001-4通信原理实验系统由函数信号源模块、PCM/PAM模块、复接/解复接模块、线路编/解码及锁相环模块、CVSD编/解码模块、FPGA与DSP初始化模块、数字信号处理模块、AD/DA与调制/解调模块以及显示控制模块人机界面等9个基本功能模块组成。

学生通过自行连接信号线贯通各基本模块,构建完整的通信系统,检验和调整各个关键点的信号,可大大加深对现代通信系统概念和结构的理解。在本系统中,包含两套不对称的传输信道,这样做的目的是为了尽可能多的涵盖通信传输系统各方面的技术。

主要体现无线信道传输技术的传输信道,信号流程为:模拟函数信号源→CVSD话音编码或误码仪的码型信号发生器数字调制信道数字解调CVSD话音译码示波器显示或误码仪的误码检测器。主要体现有线信道传输技术的信号支路。